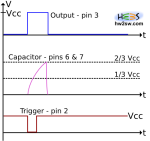

We're talking again of the monostable configuration: the timing calculation is the matter.

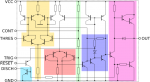

First of that we'd do better to have a closer look at the timing aspects.

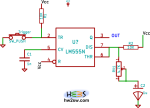

As clearly seen the couple resistor-capacitor in input to pin 6 fixes the amount of time during which the output is high.

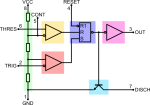

The simple multiplication returns a time dimension, but it must be corrected by a factor (a constant) to be determined.

To do this please refer to the above image: again we have a temporal diagram with a hypothetical flow of signals involved, for a non-retriggerable monostable.

Now the time is the main matter: how to determine a correct value for the tON at output?